Page 37 - CITS - Electronic Mechanic - TT - 2024

P. 37

ELECTRONICS MECHANIC - CITS

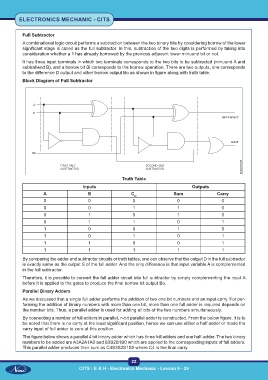

Full Subtractor

A combinational logic circuit performs a subtraction between the two binary bits by considering borrow of the lower

significant stage is called as the full subtractor. In this, subtraction of the two digits is performed by taking into

consideration whether a 1 has already borrowed by the previous adjacent lower minuend bit or not.

It has three input terminals in which two terminals corresponds to the two bits to be subtracted (minuend A and

subtrahend B), and a borrow bit Bi corresponds to the borrow operation. There are two outputs, one corresponds

to the difference D output and other borrow output Bo as shown in figure along with truth table.

Block Diagram of Full Subtractor

Truth Table

Inputs Outputs

A B C in Sum Carry

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

By comparing the adder and subtractor circuits or truth tables, one can observe that the output D in the full subtractor

is exactly same as the output S of the full adder. And the only difference is that input variable A is complemented

in the full subtractor.

Therefore, it is possible to convert the full adder circuit into full subtractor by simply complementing the input A

before it is applied to the gates to produce the final borrow bit output Bo.

Parallel Binary Adders

As we discussed that a single full adder performs the addition of two one bit numbers and an input carry. For per-

forming the addition of binary numbers with more than one bit, more than one full adder is required depends on

the number bits. Thus, a parallel adder is used for adding all bits of the two numbers simultaneously.

By connecting a number of full adders in parallel, n-bit parallel adder is constructed. From the below figure, it is to

be noted that there is no carry at the least significant position, hence we can use either a half adder or made the

carry input of full adder to zero at this position.

The figure below shows a parallel 4 bit binary adder which has three full adders and one half-adder. The two binary

numbers to be added are A3A2A1A0 and B3B2B1B0 which are applied to the corresponding inputs of full adders.

This parallel adder produces their sum as C4S3S2S1S0 where C4 is the final carry.

22

CITS : E & H - Electronics Mechanic - Lesson 9 - 29