Page 48 - CITS - Electronic Mechanic - TT - 2024

P. 48

ELECTRONICS MECHANIC - CITS

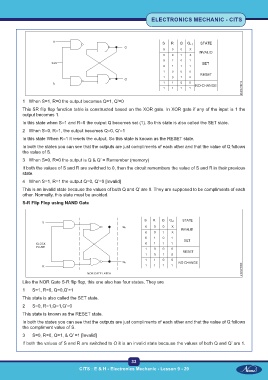

1 When S=1, R=0 the output becomes Q=1, Q’=0

This SR flip flop function table is constructed based on the XOR gate. In XOR gate if any of the input is 1 the

output becomes 1.

In this state when S=1 and R=0 the output Q becomes set (1). So this state is also called the SET state.

2 When S=0, R=1, the output becomes Q=0, Q’=1

In this state When R=1 it resets the output. So this state is known as the RESET state.

In both the states you can see that the outputs are just compliments of each other and that the value of Q follows

the value of S.

3 When S=0, R=0 the output is Q & Q’ = Remember (memory)

If both the values of S and R are switched to 0, then the circuit remembers the value of S and R in their previous

state.

4 When S=1, R=1 the output Q=0, Q’=0 [Invalid]

This is an invalid state because the values of both Q and Q’ are 0. They are supposed to be compliments of each

other. Normally, this state must be avoided.

S-R Flip Flop using NAND Gate

Like the NOR Gate S-R flip flop, this one also has four states. They are

1 S=1, R=0, Q=0,Q’=1

This state is also called the SET state.

2 S=0, R=1,Q=1,Q’=0

This state is known as the RESET state.

In both the states you can see that the outputs are just compliments of each other and that the value of Q follows

the compliment value of S.

3 S=0, R=0, Q=1, & Q’ =1 [Invalid]

If both the values of S and R are switched to O it is an invalid state because the values of both Q and Q’ are 1.

33

CITS : E & H - Electronics Mechanic - Lesson 9 - 29