Page 49 - CITS - Electronic Mechanic - TT - 2024

P. 49

ELECTRONICS MECHANIC - CITS

They are supposed to be compliments of each other. Normally, this state must be avoided.

4 S=1, R=1,Q & Q’= Remember

If both the values of S and Rare switched to 1, then the circuit remembers the value of S and R in their previous state.

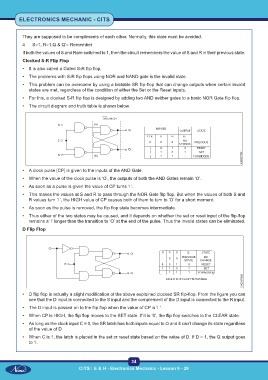

Clocked S-R Flip Flop

• It is also called a Gated S-R flip flop.

• The problems with S-R flip flops using NOR and NAND gate is the invalid state.

• This problem can be overcome by using a bistable SR flip-flop that can change outputs when certain invalid

states are met, regardless of the condition of either the Set or the Reset inputs.

• For this, a clocked S-R flip flop is designed by adding two AND neither gates to a basic NOR Gate flip flop.

• The circuit diagram and truth table is shown below.

• A clock pulse [CP] is given to the inputs of the AND Gate.

• When the value of the clock pulse is ‘O’, the outputs of both the AND Gates remain ‘O’.

• As soon as a pulse is given the value of CP turns ‘l ‘.

• This makes the values at S and R to pass through the NOR Gate flip flop. But when the values of both S and

R values turn ‘l ‘, the HIGH value of CP causes both of them to turn to ‘O’ for a short moment.

• As soon as the pulse is removed, the flip flop state becomes intermediate.

• Thus either of the two states may be caused, and it depends on whether the set or reset input of the flip-flop

remains a’ l’ longer than the transition to ‘O’ at the end of the pulse. Thus the invalid states can be eliminated.

D Flip Flop

• D flip flop is actually a slight modification of the above explained clocked SR flip-flop. From the figure you can

see that the D input is connected to the S input and the complement of the D input is connected to the R input.

• The D input is passed on to the flip flop when the value of CP is ‘l ‘.

• When CP is HIGH, the flip flop moves to the SET state. If it is ‘0’, the flip flop switches to the CLEAR state.

• As long as the clock input C = 0, the SR latch has both inputs equal to O and it can’t change its state regardless

of the value of D

• When C is 1, the latch is placed in the set or reset state based on the value of D. If D = 1, the Q output goes

to 1.

34

CITS : E & H - Electronics Mechanic - Lesson 9 - 29