Page 50 - CITS - Electronic Mechanic - TT - 2024

P. 50

ELECTRONICS MECHANIC - CITS

If D = 0, the Q output goes to 0.

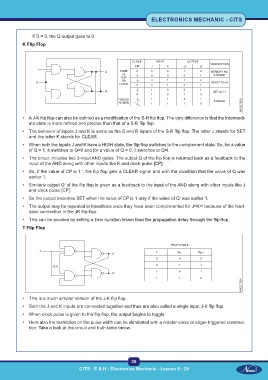

K Flip Flop

• A J-K flip flop can also be defined as a modification of the S-R flip flop. The only difference is that the intermedi-

ate state is more refined and precise than that of a S-R flip flop.

• The behavior of inputs J and K is same as the S and R inputs of the S-R flip flop. The letter J stands for SET

and the letter K stands for CLEAR.

• When both the inputs J and K have a HIGH state, the flip-flop switches to the complement state. So, for a value

of Q = 1, it switches to Q=0 and for a value of Q = 0, it switches to Q=l.

• The circuit includes two 3-input AND gates. The output Q of the flip flop is returned back as a feedback to the

input of the AND along with other inputs like K and clock pulse [CP].

• So, if the value of CP is ‘l ‘, the flip flop gets a CLEAR signal and with the condition that the value of Q was

earlier 1.

• Similarly output Q’ of the flip flop is given as a feedback to the input of the AND along with other inputs like J

and clock pulse [CP].

• So the output becomes SET when the value of CP is 1 only if the value of Q’ was earlier 1.

• The output may be repeated in transitions once they have been complimented for J=K=l because of the feed-

back connection in the JK flip-flop.

• This can be avoided by setting a time duration lesser than the propagation delay through the flip-flop.

T Flip Flop

• This is a much simpler version of the J-K flip flop.

• Both the J and K inputs are connected together and thus are also called a single input J-K flip flop.

• When clock pulse is given to the flip flop, the output begins to toggle.

• Here also the restriction on the pulse width can be eliminated with a master-slave or edge• triggered construc-

tion. Take a look at the circuit and truth table below.

35

CITS : E & H - Electronics Mechanic - Lesson 9 - 29