Page 34 - CITS - Electronic Mechanic - TT - Hindi

P. 34

इले ॉिन मैके िनक - CITS

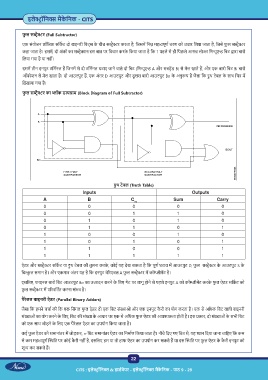

फु ल स ट ै र (Full Subtractor)

एक संयोजन लॉिजक सिक ट दो बाइनरी िबट्स के बीच स ट ै र करता है, िजसम िन मह पूण चरण को उधार िलया जाता है, िजसे फु ल स ट ै र

कहा जाता है। इसम , दो अंकों का स ट ै न इस बात पर िवचार करके िकया जाता है िक 1 पहले से ही िपछले आस लोअर िम ूए िबट ारा बारो

िलया गया है या नहीं।

इसम तीन इनपुट टिम नल ह िजनम से दो टिम नल घटाए जाने वाले दो िबट (िम ूए A और सबट ड B) से मेल खाते ह , और एक बारो िबट Bi बारो

ऑपरेशन से मेल खाता है। दो आउटपुट ह , एक अंतर D आउटपुट और दू सरा बारो आउटपुट Bo के अनु प है जैसा िक थ टेबल के साथ िच म

िदखाया गया है।

फु ल स ट ै र का ॉक डाय ाम (Block Diagram of Full Subtractor)

थ टेबल (Truth Table)

Inputs Outputs

A B C in Sum Carry

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

ऐडर और स ट ै र सिक ट या थ टेबल की तुलना करके , कोई यह देख सकता है िक पूण घटाव म आउटपुट D, फु ल स ट ै र के आउटपुट S के

िब ु ल समान है। और एकमा अंतर यह है िक इनपुट वे रएबल A फु ल स ट ै र म कॉ ीम ट है।

इसिलए, फाइनल बारो िबट आउटपुट Bo का उ ादन करने के िलए गेट पर लागू होने से पहले इनपुट A को कॉ ीम ट करके फु ल ऐडर सिक ट को

फु ल स ट ै र म प रवित त करना संभव है।

पैरेलल बाइनरी ऐडर (Parallel Binary Adders)

जैसा िक हमने चचा की िक एक िसंगल फु ल ऐडर दो एक िबट सं ाओं और एक इनपुट कै री का योग करता है। एक से अिधक िबट वाली बाइनरी

सं ाओं का योग करने के िलए, िबट की सं ा के आधार पर एक से अिधक फु ल ऐडर की आव कता होती है। इस कार, दो सं ाओं के सभी िबट

को एक साथ जोड़ने के िलए एक पैरेलल ऐडर का उपयोग िकया जाता है।

कई फु ल ऐडर को समानांतर म जोड़कर, n-िबट समानांतर ऐडर का िनमा ण िकया जाता है। नीचे िदए गए िच से, यह ान िदया जाना चािहए िक कम

से कम मह पूण ित पर कोई कै री नहीं है, इसिलए हम या तो हाफ ऐडर का उपयोग कर सकते ह या इस ित पर फु ल ऐडर के कै री इनपुट को

शू कर सकते ह ।

22

CITS : इले ॉिन & हाड वेयर - इले ॉिन मैके िनक - पाठ 9 - 29