Page 32 - CITS - Electronic Mechanic - TT - Hindi

P. 32

इले ॉिन मैके िनक - CITS

पाठ 9 - 29: कॉ नेशनल लॉिजक सिक ट (Combinational Logic Circuit)

उ े

इस पाठ के अंत म आप यह जान सक गे

• िविभ लॉिजक सिक ट जैसे िक हाफ एडर, फु ल एडर, एनकोडर आिद को बता सक गे।

• प ॉप के िविभ कार और उनके अनु योग बता सक गे

• के यरलेस और उनके कारों के बारे म बता सक गे।

बाइनरी एिडशन सिक ट (Binary Addition Circuits)

दो बाइनरी नंबरों को जोड़ने का ऑपरेशन िडिजटल कं ूटर ारा िकए जाने वाले मूलभूत काय म से एक है। चार बेिसक जोड़ ऑपरेशन 0 + 0 = 0,

1 + 0 = 1, 0 + 1 = 1 और 1 + 1 = 10 ह । पहले तीन ऑपरेशन म , ेक बाइनरी एिडशन एक िबट के प म योग देता है, यानी, या तो 0 या 1।

लेिकन चौथा एिडशन ऑपरेशन एक ऐसा योग देता है िजसम दो बाइनरी अंक होते ह । जोड़ के ऐसे प रणाम म , लोअर िस ीिफक ट िबट को सम िबट

कहा जाता है, जबिक हाइयर िस ीिफक ट िबट को कै री िबट कहा जाता है। दो बाइनरी नंबरों को जोड़ने के िलए िडज़ाइन िकए गए लॉिजक सिक ट को

बाइनरी एडर सिक ट कहा जाता है।

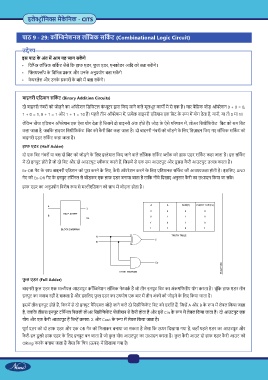

हाफ एडर (Half Adder)

दो एक िबट नंबरों या बस दो िबट को जोड़ने के िलए इ ेमाल िकए जाने वाले लॉिजक सिक ट ॉक को हाफ एडर सिक ट कहा जाता है। इस सिक ट

म दो इनपुट होते ह जो दो िबट और दो आउटपुट ीकार करते ह , िजसम से एक सम आउटपुट और दू सरा कै री आउटपुट उ करता है।

Ex-OR गेट के साथ बाइनरी एिडशन को पूरा करने के िलए, कै री ऑपरेशन करने के िलए एिडशनल सिक ट की आव कता होती है। इसिलए, AND

गेट को Ex-OR गेट के इनपुट टिम नल से जोड़कर एक हाफ एडर बनाया जाता है तािक नीचे िदखाए अनुसार कै री का उ ादन िकया जा सके ।

हाफ एडर का अनु योग िवशेष प से म ीएिडशन को साथ म जोड़ना होता है।

फु ल एडर (Full Adder)

बाइनरी फु ल एडर एक म ीपल आउटपुट कॉ नेशन लॉिजक नेटवक है जो तीन इनपुट िबट का अंकगिणतीय योग करता है। चूंिक हाफ एडर तीन

इनपुट का जवाब नहीं दे सकता है और इसिलए फु ल एडर का उपयोग एक बार म तीन अंकों को जोड़ने के िलए िकया जाता है।

इसम तीन इनपुट होते ह , िजनम से दो इनपुट वै रएबल जोड़े जाने वाले दो िस ीिफक ट िबट को दशा ते ह , िज A और B के प म लेबल िकया जाता

है, जबिक तीसरा इनपुट टिम नल िपछली लोअर िस ीिफक ट पोजीशन से कै री होता है और इसे Cin के प म लेबल िकया जाता है। दो आउटपुट एक

योग और एक कै री आउटपुट ह िज मशः Σ और Cout के प म लेबल िकया जाता है।

पूण एडर को दो हाफ एडर और एक OR गेट को िमलाकर बनाया जा सकता है जैसा िक ऊपर िदखाया गया है, जहाँ पहले एडर का आउटपुट और

कै री-इन दू सरे हाफ एडर के िलए इनपुट बन जाता है जो कु ल योग आउटपुट का उ ादन करता है। कु ल कै री आउट दो हाफ एडर कै री आउट को

ORing करके बनाया जाता है जैसा िक िच (ऊपर) म िदखाया गया है।

20